#### BINARY SYSTEMS

Digital Systems:

A Digital system is defined as an interconnection of digitalmodules that manipulate discrete elements of information which is represented internally in the binary form.

Digital systems are playing a vital note in our daily life because of which we are netering the present technological period as digital age.

Fort and neliable solutions using switching techniques proved the tremendous power and wefulness of digital systems.

Digital Systems are used in communication, business transaction traditic Control, Space craft guidance, medical treatment, weather monitoring, the internet and many other commercial, industrial and scientific enterprises. Today we are enjoying digital telephones digital telephones digital telephones because of the development in digital technology.

These devices have Graphical user Interfaces (GUI's), which makes the user to interact with the digital system easily by making the choices from the Menu (ex) a group of i cons.

A GUI is nothing but a program that is written by the usen according to the application.

the characteristics of the digital systems in given below.

# Characteristics of a digital system:

- \* Digital System manipulates dyscrete elements of information.

- \* Discrete elements of information is nothing but digits such as lo decimal digits, 26 letters of alphabets and so on.

- \* In most of the digital systems the signals contain only two Values only, they one o, 1. Since they are having only two Values in number system, are can can the number system as binary number system.

- \* Discrete elements of information are represented with a group of bits called binary codes, where a bit represents a binary digit (either o'or i'). For example the decimal digits o to 9 are represented in a digital system with a 4-bit code called BCD (Binary Coded Decimal)

- \* Digital Systems like a digital computer ix a programmable device which can be programmed to perform a variety of tasks.

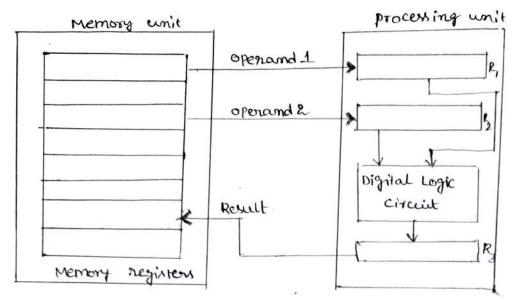

- If The digital system like a digital computer ix an interconnection of digital modules. The major cunits of a digital computer are a central processing cunit, memory cunit and input output cunit. The CPU perbound the arithmetic and logical operations. The programs and data prepared by the user can be entered into the system through an input device called keyboard and stored in the memory. The monitor and printer are the examples for output devices.

# Advantages of Digital systems over Amalog systems:

- Elexibility: Digital systems one more flexible to design as it's design involves a set of logical steps. A digital system can be neconfigured for some other application simply by changing the software program. Where as in analog systems if we want to perborm any other operation we have to change the hard whre components.

- 2) Ease of design: Digital systems are easy to design than amaly.

- Accuracy: The accuracy of the digital systems is much higher than that of the analog systems. In analog systems the temperature variations and component tolerance etc are major problems due to which the high accuracy is not possible in analog systems

- Size and neliability: The digital systems are small in size more reliable and less expensive when Compare to analog systems

- programmability: Now-a-days, digital design is carried out by writing programs in handware description language (HDL).

These languages allow to stimulate and test the perbolimance of digital Cincuity. This feature is very useful in designing critical digital systems.

- Reproducibility of the result: The output of analog systems vory with temperature, component aging, power supply vortage component tolerance and other factors. So it is difficult to produce the same nexult every time even with same set of inputs and Cincuits components. This is not the case with adjital systems. They always produce exactly same nexults with same

set of imputs and circuit components.

Dupgrading Technology: At digital technology is becoming more and more popular, more nexearch is going on in this field.

so, the technological upgrade is expected in the digital world.

### Number systems:

number system is the basis of counting various items.

On hearing the term 'number all of us are familiar with decimal number system that includes ten digits: 0,1,2,3,4,5,6,7,8 and 9.

Modern computers are operated and communicated with binary number system that includes only two digits: 0,1.

For example let us take a decimal number (24). This number can be represented in birary as (1000)2. In this example, for decimal number (24) are nequire two digits and it's birary equivalent number (11000)2 require five digits. As we go on increasing the decimal number value the number of binary digits in it's equivalent himary number will also be increasing.

This fact gives rise to three new number systems that represent a linary number in a compressed form. They are

- i) octal

- 2) Hera Decimal

- 3) Binooy Coded Decimal (BCD).

These number systems are widely used to Compress the long. Strings of linary number.

#### Radix: (or) Base:

It specifies the number of symbols used for a particular number system.

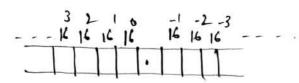

### Radix Point:

In any number system, the radix point specifies the dividing line between the integer part and fractional point.

## the Decimal Number System:

It the decimal number system contains ten unique symbols: 0, 1,2, 3, 4, 5, 6, 7, 8 and 9. That means the radix (or) base of the decimal number system is lo.

In decimal number system we can express any decimal number in terms of whits, tens, hundreds, thousands --- etc.

\* For example Let us consider a decimal number (5678.2), It can be nepresented as

(5678.2) = 5000+600+70+8+0.2

number system or base-10 number system.

= 5x103 + 6x10+ 7x10 + 8x10 + 2x10

\*The position of a digit with reference to the decimal point determined the weight of that particular digit. The sum of all digits multiplied by the respective weights gives the total number.

In a decimal number the lebt most digit which has the highest weight is called as Most significant Digit (MSD) and the nightmost digit that has the lowest weight is called as Least Significant Digit (LSD). The decimal point separates the integer and fractional parts. It The decimal number system can also be called as radix-10

Binary Number system:

\* The base (or) nadix of this number system is 2. Hence it has two independent symbols, they are 0 and 1.

- A binary digit present in a binary number is called as a bit. A bit can be either 0 (or) 1.

- \* The binary number system can also be called as radix-2 number system.

- The binary point in a binary number seperates the integer part and fractional part.

- In binary number system the weights are expressed in terms of the powers of 2.

- \* By adding each digit multiplied by it's respective weight in the given binary number, we can obtain the decimal equivalent number.

= 1x8 + 1x4 + 0x2 + 1x1 + 1x0.5 +0x0.25 + 1x0.125

= 8+4+0+1+0.5+0+0.125

= (13.625)

Practice problems: ) convert (10111.1001), into its decimal equivalent.

- 2) Convert (+00111-10111) into it's decimal equivalent

- 3) convert (101011.11011) into it's decimal equivalent

- \* The base (or) radix of the octal number system is 8.

Hence this number system has 8 independent symbols: 0, 1,2,

3, 4, 5, 6 and 7.

- \* This number system is also called as base -8 (or) radix-8 number system.

- \* In the octal number system the weights are represented in terms of Powers of 8.

---8888 5888---

\* By adding each digit of an octal number multiplied by it's respective weight we can obtain the decimal equivalent of the given octal number.

Example: Convert (2763.45) into it's equivalent decimal.

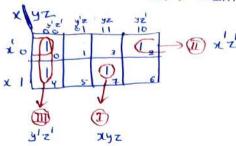

Sd (2763.45) = 2x8 + 7x8 + 6x8 + 3x8 + 4x8 + 5x8<sup>2</sup>  $(2763.45) = 2x8^3 + 7x8 + 6x8 + 3x8 + 4x8$

= 1024 + 448 + 48 + 3 + 0.5 + 0.078125

= (1523.578125)10.

practice problems: convert the following octal numbers into their respective decimal equivalent numbers

i) (762.345) ii) (3467.25) iii) (675.36)

### Hexa Decimal Number system:

- \* The base (or) radix of the hexadecimal number system is 16.

Hence this number system has 16 independent symbols: 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E and F.

- \* This number system is also called as base-16 number system (60)

nadix-16 number system.

\* In the hera decimal number system the weights one represented in terms of Powers of 16.

\* By adding each digit in the given heradecimal number multiplied by it's nespective weight we can obtain the decimal equivalent for the given heradecimal number.

Example: convert (9DEB.7A) into it's equivalent decimal number  $\{9DEB.7A\}_{16}$  into it's equivalent decimal number  $\{9DEB.7A\}_{16}$  =  $9\times16+13\times16+14\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11\times16+11$

= 36864 + 3328 + 224 +11 + 0.4375 + 0.0390625 = (40427.4765625)

practice problems: convert the following hera decimal numbers into their respective decimal equivalent numbers.

i) (687.A2) (ii) (96E.2F) (iii) (479.BD) (6

Note: \* A group of 4 binary bits is called as a Nibble \*

\* A group of 8 binary bits is called as a Byte.

\* A group of 16 binary bits is called as a word.

\*\*\* For Radix-1 number system the weights are interms of powers of n'

By adding each digit multiplied by it's respective weight we an obtain

it's decimal equivalent.

- systems. In this table the first 16 numbers present in the decimal, binary, octal and heradecimal number systems are listed.

| Decimal<br>(Base-10) | Binary<br>(base-2) | octal<br>(base-8) | Hexa becimal<br>(Base-16) |

|----------------------|--------------------|-------------------|---------------------------|

| 0                    | 0000               | 00                | . 0                       |

| 1                    | 0001               | 01                | 1                         |

| a                    | 0010               | 02                | 2.                        |

| 3                    | 0011               | 03                | 3                         |

| 4                    | 0100               | 04                | 4                         |

| 5                    | 0101               | 05                | 5                         |

| 6                    | 0110               | 06                | 6                         |

| 7                    | 0111               | 07                | 7                         |

| 8                    | 1000               | 10                | 8                         |

| 9                    | 1001               | ( )               | 9                         |

| 10                   | 1010               | 12                | Ð.                        |

| 11                   | 1011               | 13                | В                         |

| 12                   | 1100               | 14                | С                         |

| 13                   | 1101               | 15                | D                         |

| 14                   | 1110               | الد               | E                         |

| 15                   | 1173               | 17                | F                         |

## Counting in radix - n (or) base - n:

In Previous discussion we have seen the number systems with nadix equal to 10, 2, 8 and 16. Each number system has It set of symbols. For example decimal number system has nadix to and 10 set of symbols from 0 to 9. In binary system is inequal to 2 and it has 2 symbols from 0 to 1 (i.e 0,1).

In general we can say that, a number represented in radix - n, has n symbols in it's set and n can be any value.

For a particular radia value, the respective symbol set is shown in the below table.

|     | Radix-r (or) Base-r | Symbols in set.                                |  |

|-----|---------------------|------------------------------------------------|--|

|     | 2 (Binory)          | 0, 1                                           |  |

|     | 3                   | 0,1,2                                          |  |

|     | 4                   | 0, 1, 2, 3                                     |  |

|     | 5                   | 0,1,2,3,4                                      |  |

|     | 6                   | 0, 1, 2, 3, 4, 5                               |  |

|     | 7                   | 0,1,2,3,4,5,6                                  |  |

|     | 8 (octal)           | 0;1,2,3,4,5,6,7                                |  |

|     | 9                   | 0, 1, 2, 3, 4, 5, 6, 7, 8                      |  |

|     | 10 (Decimal)        | 0,1,2,3,4,5,6,7,8,9                            |  |

|     | Ĭ1 :                | 0,1,2,3,4,5,6,7,8,9,A                          |  |

|     | 12                  | 0,1,2,3,4,5,6,7,8,9,A,B                        |  |

|     | 13                  | 0,1,2,3,4,5,6,7,8,9,A,B,C                      |  |

|     | 14                  | 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D       |  |

|     | 15                  | 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E    |  |

|     | 16                  | o, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F |  |

| - 1 | 2 1                 |                                                |  |

# Converting any nadir number to decimal:

Decimal equivalent number =  $A_{m-1} n^{m-1} + A_{m-2} n^{m-2} + \cdots + A_{2} n^{2} n^{2} n^{2} n^{2} + \cdots + A_{2} n^{2} n^$

Extemple: convert (3102.12) to it's equivalent decimal.

Sol) Given (3102.12) which has radix 4. Hence the weight are assigned in terms of Powers of 4.

43444 414 4142 (3102.12)

The decimal equivalent number for  $(3102.12)_{4}$  is  $= 3x4^{3} + 1x4^{2} + 0x4^{4} + 2x4^{6} + 1x4^{4} + 2x4^{2}$   $= (210.375)_{10}$   $\therefore (3102.12)_{4} = (210.375)_{10}$

Practice problems: convert the following into their equivalent decimal.

i) (231.23), ii) (310.21) [11] (123.15)

Example convert (654.32) to it's equivalent decimal.

Soi) Since the given number  $(654.32)_{7}$  has the radix -7, the weights are auxigned in terms of toward of 7.  $\frac{7}{4} + \frac{1}{4} + \frac{7}{4} + \frac{7}{4} = 6x + 7 + 5x + 7 + 4x + 3x + 7 + 2x + 7$

= (333.4693878)

Practice problems convert i) (A98.7B) to it's equivalent decimal ii) (786.35) to it's equivalent decimal.

#### Number base conversions:

## Binary to octal Conversion;

we know that the base for octal number system is 8 and the base for binary number system is 2. The base for octal number is the third Power of the base for binary. (i.e. 8=3). Therefore by grouping 3 digits of binary numbers and then conventing each group to it's octal equivalent, we can convert the given binary number to it's octal equivalent.

Example: Convert (10101101.0111) to octal equivalent.

<u>Solution</u>: Given binary (10101101.0111)2.

To convert a binary number to octal equivalent we need to follow the steps given below.

step1: Make groups of 3-bits starting from night most bit for integer part and Lebt most bit for fractional Part append 0's at the end it necessary.

Stepa: write the equivalent octal number for each group of 3-6ith.

step1: 010 101 101, 011 100

Steph: 2 5 5 . 3 4

·· (10101101:0111) = (255.34)

#### practice problems:

convert the following binary numbers to their equivalent octal numbers

i) (11001101111.01011) ii) (1010111011.101111)2

The octal to binary conversion is a neverse process of the Conversion of binary to octal. In this actal to binary conversion, each octal digit in the given octal number 1/2 neplaced by it's 3 bit binary equivalent to get the binary equivalent of it.

Example: convert (367.04) to it's equivalent binary number.

Sol) Given the octal number (367.04).

To convert the given octal number to binary we need to follow the steps given below.

Step1: white the equivalent 3-bit binary number for each octal digit in the given octal number.

Step 1: Remove leading and trailing 0's from the integer - part and fractional Parts respectively (if any)

3 6 7 . 0 4

Step 1: 011 110 111 , 000 100

step2: 11110111.0001

:. (367.04) = (11110111.0001)

Practice Problems: convert the following octal numbers to their equivalent binary numbers. i) (73.465) ii) (125.62) 8

Example: convert (35.764) to it's equivalent binary.

Set given octal number is (35.764).

step1: 011 101. 111 110 100

Step 2: 11101 · 1111101

.. (35.764) = (11101. 111101)

## Binary to Hera decimal Conversion:

we know that the base of the henadecimal number system is 16 and the base of the binary number system is 2. The base of the hexadecimal number is the fourth power of the base for the binary numbers. Therefore by grouping 4 digits of binary numbers and then Converting each group to it's hexadecimal equivalent we can convert binary number to it's hexadecimal equivalent.

Sumple: convert (1101110110011.1010110110), & it's heradecimal equivalent.

Sol) Given binary number (1101110110011.1010110110),

To convert a binary number to it's hexadecimal equivalent we need to follow the following steps.

step1: make the group, of 4 bits starting from night most bit for integer part and lebt most bit for fractional parts append o's at the end if necessary.

Steph: write the equivalent hexadecimal number for each group of 4-6its.

Step1: 0001 | 1011 | 1011 | 0011 . 1010 | 1101 | 1000

### practice problems:

(0 1001 1011 1110.011111) ii) (1010 11011.100101) (10101110 . 1001010) (10101110 . 10010101)

The nexadecimal to binary conversion in the reverse process of the Conversion of binary to hexadecimal. In this hexadecimal to binary conversion, each hexadecimal digit in the given hexadecimal mumber is replaced by it's 4-bit binary equivalent to get the binary equivalent to

Example: Convert (706.BA) to it's equivalent binary number.

sol)

Given the hexadecimal number (706.BA).

To convert the given heradecimal number to binary we need to follow the steps given below.

each digit in the given herea decimal number.

Step2: Remove the leading and trailing o's from the integer part and fractional Parts respectively (if any).

7 C 6 . B A Step1: 0111 1100 0110 1011 1010

step2: (11111000110.1011101)

:. (7C6.BA) = (11111000110.1011101)

Example 2: Convert (976.DAC) to it's equivalent binary number.

Sol Given hexadecimal number (976.DAC) (

Step1: 9 7 6 . D A C

Steps: (100101110110.1101101011)

:. (976. DAC) = (100101110110.1101101011)

Practice problems: convent of (GEA 5. BE) (11) (986. BED) to binary ...

## octal to Hexa decimal Conversion:

In the process to convert a given octal number to it's hera decimal equivalent, the following steps are to be followed.

- i) convert the given odal number to it's binary quivalent.

- 2) convert this binary equivalent obtained in stept to it's hera decimal equivalent

Example: Convert (617.25) to it's heradecimal equivalent.

Sol: Given octal number is (617.25)

Step1: Write the equivalent 3 bit binary number for each octal digit in the given octal number.

steps: make group of 4-bits starting from right most bit for integer part and lebt most bit for fractional part and append o's at the end if necessary.

step 3: write the equivalent hexadecimal number for each group of 4 bits.

6 1 7 · 2 5

Step1: 110 001 111 010 101

Step2:0001/1000/1111 · 0101/0100

Step3: 1 8 F · 5 4

their equivalent Heradecimal numbers.

### Hexadecimal to octal conversion:

To convert a hexadecimal number into octal, the following steps are to be followed.

- 1) Convert the given hexadecimal number to it's equivalent binary.

- 2) Convert the binary equivalent obtained in step 1 into it's octal equivalent.

Example: Convert (79D.AE) 16 into it's octal equivalent.

Set ?: Given hexadecimal number = (79D.AE)16

To convert hereadecimal to octal

- I) white the equivalent 4-bit binary number for each digit in the given herea decimal number

- 2) Make the group of 3 bits stooting from the right most bit for the integer part and the lebt most bit for the fractional part append o's at the end if required

- 3) write the equivalent octal number for each group of 361/2

7 9 D . AE

Step1: 0111 1001 1101. 1010 1110

stepz: 011 110, 011, 101. 101; 011, 100

step3: 3 6 3 5 · 5 3 4

practice problems: convert the following heradecimal number into octal equivalent. i) (BCGG. FA) (6 ii) (CD8.9F) (6 iii) (98B. EC) (6 iv) (F78G.CD) (6

## conversion of Decimal to any radix:

The convension of decimal number to any radix is carried out in two steps.

- which is accomplished by using successive division method.

- 2) The fractional part is to be convented into the desired radix which is done by using successive multiplication method.

# successive division method for integer part conversion:

The integer part of the decimal number is divided by the new radix repeated by until the quotient is zero. The remainders are taken from bottom to top to form the new radix number.

# Successive multiplication for fractional fart conversion:

the fractional part of the given decimal number is multiplied by the new readix that produces a product that has an integer part and a fractional part. The integer part is collected and the fractional part is again multiplied by the new madix. This process is continued until the fractional part is equal to This process is continued until the fractional part is equal to zero (or) until new radix number have substicient digits. The integer part of each product is to be taken from the integer part of each product is to be taken from the top to bottom to form the fractional part of the new radix number.

Example: Find the octal equivalent for the following decimal number. (659.825)

soly Given decimal number = (659.825)10 nequired radix is 8 as we need to find octal equivalent.

# Fractional Part Conversion using successive multiplication method:

0.825 x 8 = 6.6

$$\Rightarrow$$

6

0.6 x 8 = 4.8  $\Rightarrow$  4

0.8 x 8 = 6.4  $\Rightarrow$  6

0.4 x 8 = 3.2  $\Rightarrow$  3

0.2 x 8 = 1.6  $\Rightarrow$  1

Practice problems; i) convert (38475) to binary form.

ii) convert (9865.374), to it's hexadecimal equivalent.

Example: convert the following i)

$$(102.67)_8 = (?)_{12}$$

ii)  $(345.21)_6 = (?)_7$

iii)  $(A98B)_{12} = (?)_3$

To get hadir-12 number from the given octal number, firstly the octal number has to be converted into the decimal equivalent.

Now Convert this decimal equivalent number into radix-12 number.

0.859375 X12 = 10.3125

$$\Rightarrow$$

A

0.3125 X12 = 3.75  $\Rightarrow$  3

0.75 X12 = 9.00  $\Rightarrow$  9

To get radix-7 equivalent number from the fiven radix-6 number firstly convert the given radix-6 number to decimal equivalent.

mber to decimal survacons.

(3 45.21)

=

$$(37.3611111)$$

=  $(137.3611111)$

=  $(137.3611111)$

NOW convert this decimal equivalent number into radix-7.

7

$$19-4$$

2-5

10 = (254)

0.3611111

$$\times 7 = 2.52737777 \Rightarrow 2$$

0.5277777  $\times 7 = 3.6944439 \Rightarrow 3$

0.6944439 $\times 7 = 4.8611073 \Rightarrow 4$

0.8611073 $\times 7 = 6.0277511 \Rightarrow 6$

To convert radix-12 number into radix-3, firstly it has to be converted into radix-10 (i.e decimal).

$$A 98B = 10 \times 12^{3} + 9 \times 12^{2} + 8 \times 12^{2} + 11 \times 12^{2}$$

$$= 17280 + 1296 + 96 + 11$$

$$= (18683)_{10}$$

Now convert this decimal equivalent number into it's equivalent radix-3 number.

Example: convert (76.275) to decimal and then to binary. Zar  $(76.275)_{0} = (?)_{0}$  $8^{1}8^{0}8^{1}8^{2}8^{3}$   $7^{1}275 = 7x8 + 6x8 + 2x8^{1} + 7x8 + 5x8^{3}$ = (62,369140625) (62.369140625) has to be converted to binary. 262 2 31-0 1 2 15-1 2 3 -1 0.369140625X2 = 0.73828125=) 0 0.73828125x2 = 1.4765625 => 1 0.4765625 12 = 0.953125=) 0 0.953125 x2 = 1.90625 =) 1 0.90625 x 2 = \$.8125 => 1 0.8125 x 2 = 1.625 => 1 1 .. (62) = (111110)<sub>2</sub> i. (0.369140625) = (0.010111) .: (62.369 140625) = (111110.010111 101) If (79) = (17) = (142), Then find X, Y. 30() (79) = (117) x Converting (117) into decimal 117 = 1xx + 7 x x  $= x^{2} + x + 7$ given (117) x = (79) " X2+X+7 = 79 (x+9)(x-8) = 0 x = -9, x = 8x2+x+7-79 =0  $x^2 + x - 72 = 0$ Radix Connot be negative  $x^2 + 9x - 8x - 72 = 0$ x(x+9) - 8(x+9) = 0

" X=8.

Similarly, from the given problem  $(42)_y = (74)_{10}$   $1 \cdot y^2 + 4 \cdot y + 2y^0 = 79$   $\Rightarrow y^2 + 4y - 77 = 0$   $y^2 + 11y - 7y - 77 = 0$  y(y+11) - 7(y+11) = 0 (y-7)(y+11) = 0y = 7 : y = -11

Radia Cannot be negative. SO Y=7.

.. X=8 , Y=7 ·

Example: (143) = (x), Then x =?

Sol) First of all convert (143) to decimal.

(143) = 1x52 + 4x51 + 3x5

=) (143) = (48) 10

NOW  $(48)_{10} = (x)_6$ , to get x value perform successive division with 6.

6/48

: (48) = (120) , X = 120.

Complements:

In digital computers, to simplify the subtraction operation and for logical operations complements are used.

In each radix system, there are two types of complements. They are is Radix complement as Diminished radix complement.

The tradix Complement is referred as 21's complement and the diminished tradix Complement is referred as 21-1's complement.

For example in binary system the radix is a. so the two Possible Complements in the binary number system are

2's complement and i's complement. In Decimal number - system we have lo's complement and 9's complement.

In octal we have the 8's complement and 7's complement. In hexadecimal we have 16's complement and 15's complement.

i's complement representation

the is comprement of a given binary number is obtained by replacing all is with o's and all o's with i's.

The 1's complement of a binary number is obtained by subtracting each bit of the given binary number from 1.

2's complement representation:

The l's complement of a given binary number it obtained by adding 1 to the LSB of the 1's complement of that number. Example:

Find the 1's complement and l's complement of the following

Find the is complement and a's complement of the following binary numbers. i> 10110110 ii> 11001011

Sol) i) given binary number = (10110110)2 1's complement = 01001001

2's complement = 01001001

... 2's complement = 0100 1010

(i) Given binary number = (100 1011)2 1's complement = (0011 0100) 2's complement = 0011 0100

: 2's complement = 0011 0101

The digital computers will perboism various arithmetic operations and logical operations. The bossic arithmetic operations in the sinary one 1. Binary Addition 2. Binary Subtraction 3. Binary Multiplication and 4. Binary Division.

## Binary Addition:

The binary addition involves the four elementary operations given below. i) 0+0=0

Example: Perborm the binary addition between (11001011) (1101010)

Sol)

Given binary numbers are (11001011) and (11011010)

Example: Add (28), and (15), by conventing them to binary.

$$2 \frac{28}{2 \cdot 1 \cdot 0}$$

$$2 \frac{14-0}{2 \cdot 3-1}$$

$$2 \frac{3-1}{3-1}$$

$$3 \frac{3-1}{3-1}$$

$$3$$

#### Binary Subtraction:

The binary subtraction includes four basic operations.

They are

$$i > 0-0=0$$

$i > 0-1=1$  with borrow 1

$i > 1-0=1$

$i > 1-1=0$

X - Y

X = Minuend, Y = Subtrahend

In all the four operations shown above subtrahend bit is subtracted from the minuend bit. In the second case (1-e 0-1=1 with borrow 1) the minuend bit is smaller than the subtrahend bit hence i's taken as borrow.

NOTE: It is easy to Perborm the subtraction manually by a numan being. But it is difficult to implement in a computer. So the computer uses complement methods to terborm the subtraction operation.

# Binary subtraction using its complement method:

the operation A-B is perbormed using the following steps.

- 1. Find the is complement of B.

- 2. Add i's complement of B with A.

- 3. If carry is generated the result is Poxitive and in the true form. Add carry to the result to get the final result.

- 4. If carry is not generated the result is negative and in the i's complement form. Find the 1's complement of the nexult to get the final result.

Ex: Perform (88) 10-15) 10 using i's complement method.

Sol) Given number one

$$(28)_{10}$$

and  $(15)_{10}$   $(28)_{10} = (11100)_{2}$   $(15)_{10} = (1111)_{2}$

The number of bits in the binary equivalent of (88) 10 is five where as in (15) it is four. So append a 0 in the left side of the binary equivalent of (15) to make it 5 bits.

1147

NOW i's complement of (15) = 10000

Adding is complement of (15), with (28), using binary addition.

11100

since carry in generated, the result is Positive and in the true form. Now add carry to the result 01100 to get the final result

Perbarm (15) - (28) 10 curing 1's complement method.

Sel) given numbers are (15), and (28).

$$(15)_{10} = (1111)_{2}$$

$(28)_{10} = (1100)_{1}$

To make the number of bits erual in both the numbers, append a zero (o) in the relt side of 15.

Now 1's complement of (28) = (1100) is (00011)2 Add the 1's complement of (21) with (15), wring binary addition

Here no carry is generated Hence the nexult is negative and in is complement form.

1's complement of 10010 is = 01101 = (13)10

Elli Perboim (31) - (19) wring 6bit 1's complement method.

numbers are (21)10 and (9)10

આ)

$$(21)_{10} = (11111)_{2}$$

,  $(19)_{10} = (10011)_{2}$

given 651t 1's complement method. So the binary equivalent of (31) and (19) should have 6 bits each. so add one zero to the lebt side of (31)10 and (19)10 to make them 6 bit.

NOW is complement of (19)10 = 101100

Add 1's complement of (19)10 with (31)10 using binary addition

since carry ingenerated menelt is Positive and in the true form, add carry to the result 001011 to get final result.

The operation A-Busing 2's complement method is Pentolmed by using the following steps.

13

> Find the 2's Complement of B.

2) Add 2'x Comprement of B with A.

3) If the carry is generated the nexult is positive and in the true film. Ignore the carry to get the final nexult.

If the carry is generated the nexult is negative and in the 2's Complement form. Find the 2's Complement of the nexult to get the final nexult.

ENO Find (37) - (25) tusing 2's Complement method.

Given numbers are (37) = (100101)

(25) = (11001)2

The number of bits in the binary of (25) is one bit less than (27). So append a zero to the lebt of (25) .

2's complement of (25) = ?

i's complement of (25) = 100110

2's complement of (25) = 100110

Adding a's complement of (25), and (27) using bishary addition

100101 100111 001100

Since a carry is generated the nexult is Positive and in true form. Discard the carry to get the final result. \*

(37) 10-85) 10 = + (001100) = + (12) 10.

Find (25) - (37) wring 2's Complement method.

Given numbers are (25) and (37) 10 ક્યે)

$$(25)_{10} = (1100)_{2}$$

To equate the number of bits in each equivalent value, append a zero to the left of (25)10.

2's complement of (37), =?

i's complement of (37) = 011010

2's Complement of (37) = 011011

Add 2's complement of (37) with (25) wsing binary addition

011001

Since carry is not generated the nesult is negative and in 2's

Complement form.

$$(25)_{10} - (37)_{10} = (-001100)_{2} = (-12)_{10}$$

## Practice problems:

Find the following using is Complement method

i) (69) - (35) (43) - (78) 10

2) Find the following using 2's complement method.

i)  $(55)_{10}$  -  $(28)_{10}$  (i)  $(39)_{10}$  -  $(48)_{10}$

#### Binary Multiplication:

the multiplication process for binary numbers is similar to the decimal numbers. Actually binary multiplication is simple than decimal multiplication, since it involves only is and o's.

This Process involves the following four elementary operations.

Oxo = 0

0 = 1 X D

1 x0 = 0

111 = 1

Ex: multiply (1101) by (101) wring sinary multiplication.

sol) Here we need to find (10) x(0),

Here (101) is multiplicand and (01) is multiplier.

1101 X 101

$(1101)_2 \times (101)_2 = (10000001)_2 = (65)_{10}$

Ex: multiply (101.11) and (110.01) wing binary multiplication.

Sol).

101.11 × 110.01

Fractional digita in the multiplication nesult = Fractional digits in the multiplicand + Fractional digits in the multiplican.

$$= 2+2$$

$$= 4$$

$$\therefore (101.11)_{2} \times (110.01)_{2} = (100011.1111)_{2} = (35.9375)_{10}$$

bineary multiplication.

## Binory Division:

numbers. In binary division, division by a has no meaning.

The two elementary operations of binary division are

0:1=0

1:1-1

Ex: Divide (1101101) by (110),

quotient = (100100), Remainder = (11),

Practice problems: find is (10101101) - (100) is (110101011) - (111)2

#### signed Binary Numbers:

In practice, we use plus (+) sign to represent a Positive number and minus (-) sign to represent a negative number. But in Computery due to some limitations, both Positive and negative numbers are represented with only binary digits.

In general any binary number may belong to any one of these two categories given below.

1. Un signed Linary rumbers

2. Signed Limary numbers.

An unsigned binary number always represent positive number. where as in signed binary number, the number can be either positive

or negative, inc rest that bit in the signed binary number supresents the sign of the number. If the sign bit is o il nepresents the number of positive and if the sign bit is 1 it represents the number to be negative.

# The Signed binary numbers one represented in a format called signed magnitude form.

In a signed bimary number the left most bit lie MSB) represents the sign of the number and all the remaining bits represent the magnitude of the number. Some of the 8 bit signed numbers are given below.

> +6 = 00000110 -14 = 1000 1110 +28 = DOOIIIDO -64 = 11000000

\* In unsigned binary number at the bits represent the magnitude. If the signed binary number is negative, it can be represented

in three ways is signed magnitude form

a) signed i's complement form 3) signed 2's Complement form.

\* If the signed binary number is positive then the signed magnitude form, signed i's complement form and signed a's all are identical. Complement form

Representation of signed binary numbers using a's complement and 1's Complement:

I If the signed binary number is positive the sign bit o is placed. For such numbers 1's Complement and 2's Complement are evual to signed magnitude form.

If the signed binary number is negative, then the magnitude i's represented in i's complement (or) a's complement form and then the sign bit 1 is placed infront of MSB.

Exe Congress +51/2-51 in signed magnitude format, is complement and 2's Complement format.

given numbers are +51 and -51. <u>S</u>

magnitude of +51 = (110011)2 i) signed magnitude form of t51 is obtained by placing o' in the place of sign bit to 51.

i.e signed magnitude form of +51 = 0110011

signed i's Complement form and signed 2's complement form are identical to signed magnitude form for positive numbers.

i. Signed I's complement form of +51 = 0110011 Signed 2's complement form of +51 = 0110011.

Signed magnitude form of -51 is obtained by placing i in the place of sign bit to 51.

> i.e Signed magnitude form of -51 = 1110011 signed is Complement form of -51 = 1001100. signed a's complement form of -51 = 1001100,

1001101

Practice problems: find the is complement, as complement and signed manitude forms for the following numbers i) +75, i)-69 ii) -92

The following table shows all possible 4-bit signed binary numbers in the signed magnitude form, signed i's complement and signed a's complement form.

| Decimal        | signed as complement | signed is<br>Complement | Signed<br>magnitude |

|----------------|----------------------|-------------------------|---------------------|

| +7             | 0111                 | 0111                    | olll                |

| +6             | 0110                 | 0110                    | 0110                |

| <del>1</del> 5 | 0101                 | 0101                    | 0101                |

| 44             | 0100                 | 0100                    | 000                 |

| 43             | 0011                 | 0011                    | 0011                |

| ta             | 0010                 | 0010                    | 00 10               |

| +1             | 0001                 | 0001                    | 0001                |

| +0             | G 6000               | <b>ම</b> ලාල ල          | 0000                |

| -0             | _                    | 1111                    | 1800                |

| - 1            | 1111                 | 1110                    | 1001                |

| -2             | 1110                 | 1101                    | 1010                |

| -3             | 1101                 | 1100                    | 1011                |

| -4             | 1100                 | 10 4 1                  | 1100                |

| -5             | 1011                 | 1010                    | 101                 |

| -6             | 1010                 | 1001                    | 1110                |

| -7             | 1001                 | 1 000                   | 1113                |

| -8             | 1000                 | _                       | _                   |

7's Complement and 8's Complement:

In the octal number system the complements are 7's complement and 8's complement.

The 7's Complement of an octal neumber is obtained by subtracting each octal digit from 7.

The 8's complement of an octal number its obtained by adding I to the least significant digit of 7's complement.

Exampler: Find the 7's, 8's Complement of (243), and (1024),

sol 70 find 7's complement of (243), Subtracting each digit from 7 we get 777

: 7's complement of (243) = (534)

8's complement of (243) = 7's complement of (243) +1

- 534

2 535

To find 7's complement of (1024), we have to subtract each digit of (1024) from 7.

:. 7's complement of  $(1024)_8 = 6753$ 8's Complement of  $(1024)_8 = \frac{6753}{6754}$

Example Find the 8's complement of (365) s

sol) To get the 8's complement firstly we need to get

7's complement of (365).

7's complement of (365) = 777

7's complement of (365) = 7365

8's complement of (365) = 412 = 413

## 9's and 10's complements;

The decimal number system has 9's and 10's complements. To get the 9's complement for a decimal number, subtract each digit of the given decimal number from 9.

To get the 10's complement for a decimal number, add i to the deast significant digit of the 9's complement of that number.

## 15's and 16's Complements:

In hexa decimal number system the complements are 15's and 16's complements.

To get the 15's complement for a given herea decimal number, subtract each digit of the given haradecimal number from 15.

add 1 to the least significant digit of the 15's complement of that number.

St: Find the i) q's and lo's complement for (786), ii) 15's and 16's Complement for (98E8) 16

Sol) i) 70 get the 9's Complement for (786) subtract each digit of (786) from 9.

7-86 2 9's Complement = 213 + 1 = 214.

ii) roget the US's Complement for (BES), Subtract each doit of (2BES), from 15.

9 B E 8 6 4 1 7

ii 15's complement of

$$(9BE8)_6 = 6417$$

10's Complement of  $(9BE8)_6 = 6417$

$$\frac{6418}{6418}$$

Find i) 7's and 8's complement of (765), practice problems: ii) q's and 10's Complement of (842) 10

iii) 15's and 16's Complement of (87ED) 16

subtraction wing n's complement: Minuend - subtrahend (M-S)

- Equating the number of digita by padding appropriate number of zeros infront of the numbers.

- 2) Find the n's complement to subtrahend and add with minuend

- 3) If arry is generaled the tresult is treated as positive-and in true form. Discard the Carry to get the final result.

- 4) If the Goog is not generated the nexult is treated as negative and the nexult is present in 21's Complement form. Find the ris complement of the nexult and place a minus ( ) sign infront of it to get the final nexult.

Find (3265) - (741) wring 8's Complement Subtraction.

minuend = (3265), Subtrahend = (741),

To equate the number of digits in both Minnerd and Subbrahens add a leading zero to (741): i'e (0741).

NOW find the 8's complement to subtracted ise 0741.

For that we need 7's complement of (0741).

:.  $\frac{1}{2}$ 's Complement of  $(0741)_{p} = \frac{7777}{0741}$

8's Complement of (0741) = 7036 7037

Ex!

Sol

Adding 8's complement of (0741) to (3265).

(20)

Since carry is generated the result is positive. Discard arony to get the final result.

Example: Find the tresult of (9876) 10 - (345) using 10's complement suffraction method.

Sol To Equate the number of digits in each of the number, add a zero to (345) in leading position.

Now Minuend =  $(9876)_{10}$ , subtrahend =  $(0345)_{10}$ .

Finding 10's Complement of (0345) 1 For that we need 9's complement of (0345) 10.

10's Complement = 9654

Adding 10's Complement of (0345),0 to (876)10

Since carry is generated the result is positive. Discard arry to get the final result. ic 9531.

Example: Find  $(327)_8 - (765)_8$  using 8's complement subtraction Sol) winnered =  $(327)_8$  Subtrahend =  $(765)_8$ .

The number of digits are caual in both minuend and subtrahend so now need of adding leading repros to any one of them.

reinding s's complement of (765), for that firstly we need 7's complement of (765).

7's Complement of

$$(765)_g = 777$$

$\frac{765}{012}$

Adding 8's Complement of (765) to (327)

since Corry is not generated the result is negative and in 8's Complement form.

Finding 8's complement of the result and placing a minus sign before that gives the final result.

: 7's Complement of

$$(342) = \frac{777}{435}$$

8's Complement of

$$(342) = \frac{435}{436}$$

: final result = (436).

practice problem: Find (497) - (2563) using 10's complement method.

Example! Find

$$(7D9E) = (9CB)_{16}$$

Using 16's complement subtraction.

Winnerd =  $(709E)_{16}$ , Subtrahend =  $(9CB)_{16}$

To equale the number of digita in minuend and subtrahand add a zero to subtrahend in it's leading polition.

: Sustrahend = (09CB)

Find 16's Complement of subtracted (09 CB) .

15's Complement of (9CB) = 15 15 15 15 F & 3 4

16's Complement of (09CB) = F634 F635

Adding 16's complement of (09CB) to \$D9E)

709E OF6 35

Since Carry is generated the result is positive. Discard the carry to get the final nescut.

Practice Problem: Find (3DB) - (8EF7) 16 wing 16's complement subtraction.

Subtraction using n-1's Complement: Minuend (M) - Subtrahend (s)

- i) Equating the number of Ligits in Minuend and subtrahend by Padding appropreate number of leading zeros.

- a) Find the n-1's complement to subtrahend and add with minuen

- 3> If carry is generated the result is treated as positive and in true form. Add the carry to the least significant position of the result to get the final result.

- 4) If Grony is not generated the result is treated as negative

and in n-1's Complement form. Find the re-1's Complement of the result and place minus (-) sign to get the final result.

Example Find (763) - (245) using 7's complement thetwod.

Sel)

Minuend = (763) Subtrahend = (245).

7's Complement of Subtrahend = 777 245

Adding 7's Complement of Subtrahend With minuend

763 0532 515

since Carry is generated the nexult is positive. And carry to the least significant digit of the nexult to get the final result.

515,

:. (763) - (245) = (516) 8

Example: Find (354) - (672) wing 7's complement method.

Sor)

Minuend = (354) Subtrahend = (672) .

7's Complement of Subtrahend = 777

672

Adding 7's complement of subtrahend with minuend

354 105 461

Since no casery is generated, the result is negative and in 2's complement of the nexult in 2's complement of the nexult and place minus sign to get final result.

·1. (354)8 - (645) = -(316)8

Practice problems: Find is (476) - (73) ii) (64) - (75) cusing I's Complement method.

Example: Find (978) - (98) wring 9's Complement method.

Soi) Minuend = (978) , Subtrahend = (98)

to equate the number of zeros in both the given numbers add a leading zero to the subtrahend.

Subtrahend = (098)10

9's Complement of dustrahend = 999 098

Adding (978) with 9's Complement of nubtrahend.

978

Since Carry is generated the result is positive and in true form. Add carry to the least significant digit position of the result to get the final result.

879

1. (978) - (98) = (880) 10

Example:

Find (98D)<sub>16</sub> - (7BE)<sub>16</sub> using 15'S Complement method

Sol)

Given minuend = (98D)<sub>16</sub>, Subtrahend = (7BE)<sub>16</sub>

15'S Complement of Subtrahend = 15 15 15

7 B E

Adding (980) 16 With 15's Complement of (7BE)16

Since the Garay ix generated the result is positive god the carry to the least significant digit of the result to get the

practice problems: Find i) (179) - (96) and (69) 10 - (187) 10 wing 9's complement method: ii) (IBD) 6-(FC) and (9D) 1-(179) 16 wing 15's Complement method:

Binary codes:

• 5421

The digital data in represented, stored and transmitted as groups of binary digits. The group of binary digits is known as binary Code, that represents numbers, letters of the alphabets, special characters and special functions (or) control functions.

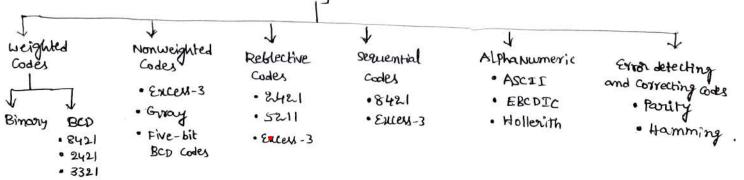

The bimary Codes one broadly classified as is weighted codes as Non weighted codes as Reblective codes 4) sequential codes as Alphanumenic codes 6> Error detecting and correcting codes.

Binary ades

### weighted codes:

In weighted codes, each digit Position of the number represents a specific weight. In weighted binary code each bit has a specific weight and each decimal digit is represented by a group of four bits.

# BCD (Binary Goded Decimal) Codes:

BCD is a numeric code in which each digit of a decimal number is represented by a seperate group of 4 bits. The most commonly used BCD code is 8421 BCD, in which each decimal digit is prepresented by a 4 bit binary number. It is called 8421 BCD because the weights associated with 4-bits are 8,4,2 and 1 from lebt to right prespectively.

| Decimal Digit | 8421 BCD |

|---------------|----------|

| 0             | 0000     |

| 1             | 0001     |

| 2             | 0010     |

| 3             | 0011     |

| 4             | 0100     |

| 7             | 0101     |

| 5             | 0110     |

| 7             | 0111     |

| 8             | 1000     |

| 9             | 1001     |

In multidigit decimal number, each decimal digit ix individually coded

$$2x$$

:  $(58)_0 = (01011000)$

Therefore total 8-bits are required to encode (8) in 8421 BCD:

when we represent the same decimal number in binary: (11010), a

we require only 6 digits. This means that representation of a decimal number in 8421 BCD is less esticient than normal binary number sumber in 8421 BCD is less esticient than normal binary number suppresentation. The advantage of a BCD code is that it is easy to convert any decimal number into BCD.

### BCD addition:

Procedure for BCD addition in given below.

- ) Add two BCD numbers using ordinary binary addition.

- 2) If 4-bit sum is equal to (or) less than 9, no correction is needed. The sum is in proper BCD form

- 3) If the 4-bit sum is greater than 9 (0) if a conry is generated from the 4-bit sum, the sum is invalid. To correct the invalid sum, add 6 i.e (0110), to the 4 bit sum. If carry results from this addition, add it to the next higher order BCD digit.

- E1: Perboin each of the following decimal additions in 8421 BCD

a) 24 + 18 b) 48 + 59

- Sd) a) given decimal numbers (24)10 and (18)10

BCD ed, ot

$$(8)^{10} = \frac{00011000}{00011000}$$

The lower nibble of the result is 1100 which is greater than 9 so add 0110 to the lower nibble to make 1100 a valid BCD.

b) sol) given decimal numbers (48), (59)10.

BCD equivalent of  $(48)_{10} = 0100 1000$ BCD equivalent of  $(59)_{10} = \frac{0101 1001}{1010 0001}$

since a away is generated from lower nibble to higher nibble add one to the lower nibble of the nexult. The higher nibble (1010), is so which is greater than 9. Hence add (0110) to the higher

BCD subtraction lying of s complement method: (procedure)

- i) Find the 9's complement of subtrahend number and add it to the minuend using BCD addition.

- 2) If carry is not generated, the nexult is negative and it is in 9's complement form. Find the 9's complement of the nexult to get the final result.

- 3) If Gorry is generated, the nexult is positive and add Gorry to the LSB to get the tinal nexult.

Example: Perboum  $(46)_{10}$  -  $(37)_{10}$  Using BCD in 9's Complement method.

Sol) Minuend =  $(46)_{10}$ , Subtrahend =  $(37)_{10}$

Adding minuend with 9's complement of subtrahend using BCD.

46 = 0100 0110

$$62 = 0110 0010$$

$$1010 1000$$

since 1010 is 79, add 0110.

since Carry is generated

negult is positive. Add this Gory to LSB,

to get final negult. 0000 1001 = 09

Example: Perboim (37) - (52) using 9's complement in BCD.

Diven minuend =  $(37)_{10}$ , Subtrachend =  $(52)_{10}$ .

Adding 9's complement of subtrahend with minuend using BCD - addition.

$$(37)_{10} = 0011 0111$$

$$(47)_{10} = 0100 0111$$

$$0111 1110$$

$$0110 0110$$

$$0110 0100$$

$$1111 0100$$

$$0100 0100$$

$$0100 0100$$

$$0100 0100$$

Since no tarry is generated, the nexult is negative and in 9's complement form.

Fractice problems: Find is (29), -(12), (i) (7), -(98), using q's Complement in BCD.

# BCD Subtraction lising 10's complement; procedure

- i) Find the 10's Complement of the subtrahend number and add it to the minuend using ECD addition.

- If carry is generated, the result is positive and in toue form discard the carry to get the final nexult.

- 3> If the Carry is not generated, the result is negative and in 10's Complement of the result to get the final neult.

Example: Find (49)10-(23) using 10's complement in BCD.

Adding minuend with lo's complement of subtrahend using BCD addition.

$$(49)_{10} = 0100 1001$$

$$(77)_{0} = 0111 0111$$

$$1100 0000 \quad \text{Since Govy is generated}$$

Since 1100 it 79 so

$$0110 \quad 0110 \quad \text{from lower nibble to higher}$$

add 0110 to lower nibble

nibble

$$1000 \quad 0110 \quad 0110 \quad \text{add 0110 to lower nibble}$$

Carry

Since carry is generated the nexult is positive and in torue Discard Conry to get the final nexult.

$$(49) - (23)_0 = (00100110)_{BCD} = (26)_0.$$

Find (23) - (59) using 10's complement in BCD. Civen minuend = (23)10 Subtrahend = (59)10. Sor)

Adding (23) 10 with 10's Complement of (59) wring BCD.

$$\frac{(23)_{10}}{(41)_{10}} = \frac{01000001}{011001000} = \frac{(64)_{10}}{01000}$$

Since no covery is generated the negative and in 10's Complement form: so 10's complement of the nevert gives the final nexult

10's Complement of

$$(64)_{10} = 9$$

's Complement of  $(64)_{10} + 1$

9's Complement of  $(64)_{10} = \frac{99}{64}_{10}$

16's Complement of  $(64)_{10} = \frac{35}{36}$

practice problems: Find i) (57)-(29) ii) (37) - (92) cusing 10's complement in BCD.

Excess-3 code (XS-3 code):

EXCENT-3 code is a modified form of a BCD number. The excent-3 code can be derived from the BeD code by adding 3 to each coded number. It is a non weighted code, self complementing and reflected code.

Pollowing table shows encert-3 codes of each decimal digit. It is a sequential code because we can get any codeward simply by adding binary 1 to it's previous code word as shown in table below

| becimal Digit | Ercen-3 Code |

|---------------|--------------|

| 0             | OO(1         |

| 1             | 0100         |

| 2             | 0101         |

| 3             | 0110         |

| 4             | 0111         |

| 5             | 1000         |

| C             | 1001         |

| <del>a</del>  | 1010         |

| 8             | 1011         |

| 9             | 1100         |

In excess-3 code we get 9's Complement of a number just by complementing each bit. Due to this excess-3 code a called as self complementing code (ar) replected Gode.

Example: Find the excess-3 code and it's 9's complement for the following decimal numbers is (592) is (03)10

Sol) is given decimal number = (592)10

Excess-3 code for (92) is = 999

Green-3 complement of (592) is = 999

Excess-3 for (407)10 = 0111 0011 1010 & other

ii given decimal number = (403)10

Excess-3 code for (402) = 0111 0011 1010 &

(i) Given decimal number = (403)<sub>10</sub>

Excess 3 Code for (403)<sub>10</sub> = 0111 0011 0110

9's complement of (403)<sub>10</sub> = 999

403

596

EXCHS-3 FOR (596) = 1000 1100 1001

NOTE: From this example it is clear that the 9's complement of a number which is in excess-3 Gode, is Simply obtained by complementing each bit in that excess-3 Gode.

#### Excess-3 addition:

To perform excess-3 addition we need to perform the steps given below.

- i) Add two excess-3 numbers using binary addition.

- 2) If carry=1 add 3 i.e (0011) to the 4-bit sum

- 3) If Coory = 0 subtract 3 from the 4-bit sum.

En: perborm is (37) 10 + (28) 10 ii) (247.6) 10 + (359.4) using encey-3 addition.

(28) 10, in excess-3 form it is = 0110 1010 (88) 10, in excess-3 form = 0101 1011 (+)  $\frac{1111}{11000101}$

From lower nibble to higher nibble a carry is generated so add (0011), to the lower nibble bits. At higher nibble no carry is

generated. so subtract (0011) from higher nibble.

(247.6) in Except 3 form = 0101 0111 1010. 1001

(359.4) in except-3 form = 0110 1000 1100.0111

1100 0000 00111 0000

Adding (0011) to the 46it sums (0000) (0111) (0000) Subtracting (0011) from 1100.

(4)0011 0011 0011

= (607)

Practice problem: Find (97) 10+(64) wing Exces-3 addition.

Excess-3 subtraction using 9's complement: (01) Excess-3 subtraction

To perborn Excess-3 subtraction we need to follow the steps given below.

- ) find the 9's complement of the subtrahend. To do this simply complement each bit in the energy-3 code of subtrahend.

- 2) Add the minuend with the 9's Complement of the hubbrahend using Excess-3 addition.

- 3) If carry=1 result is positive and in true-form. Add carry to the LSB of the result to get the final result in excess-2 form.

- 4) If carry-0 result is Ove and in 9's Complement form. Complement

27)

Example perborm the following in Enters - 3 Code wring 9's complement. (267) - (75) (57.6) - (87.8) . (bo2 i (175), in Excess-3 = 0100 1010 1000 9's complement of (175) in Excest 3=1011 0101 0111 ENCUM-3 addition (267) in Excess-3 = 0101 1001 1010

Carry 0011 0001 adding on 11 to 0000 and 0001 0011 1111 0100 0011 subtracting coll from 1111 0011 1100 0100 since carry is generated the result is positive. Add carry to LSB 1100 010 1 0011 to get the final nexult : (267) - (175) = (92) · ii)sod (87.8) in Excess-3 form = 1011 1010 . 1011 9's complement of (27.8) in Excest-3 = 01000101.0100 (57.6) in Excus-3 tom = 1000 1010. 1001 1100 1111.1101 0011 0011.0011 subtracting out from 1001 1100.1010 1100, 1111 and 1101

since no Goody is generated the nexult is negative and in 9's Complement of the nexult gives find result form. So finding the 9's Complement of the nexult = (0110 0011 · 0101) = (30.2) to 9's Complement of the nexult = (0110 0011 · 0101) = (30.2) to ...

Practice Problems: Perborn (>(27), -(65) (365), -(248), in Excess-3 code using of s comprement. Excess-3 Subtraction cusing 10's complement:

> Take ios complements of the subtrahend and add it to the minuend wing Encey-3 addition.

2) If Casay=1 the result is positive, Egnore the casary to get the

3) If Goray = 0 the result is negative. Find the 10's Complement of the neut to get the final nexult.

Example: Find i) (65) 10 -(32) 10 ii) (39) -(57) wing 10's complement Excess-3 subtraction.

(32), En Encor-3 code = 0110 0101 ાં જ્ય)

9's complement of (32) in Excest I ade Z 1001 1010

=) 10's complement of (32)0 in excess-3 = 1001 1011 } Excess-3 = 1001 1000 J addition

(65), in Encess-3 Code

00110011 Add 6011 to 0011 and 0011

since the carry is generated the result is positive. Ignore the Coary to get the final nexult.

ii sol

(57) in Encess-3 form = 1000 1010

9's complement of (52) in Excess-3 form= 0111 0101 (20) S Complement of (50) in Excest I form = 0111 0110 \x5-3 = 01101100 Jaddition (39) o in Euces-3 form Add 0011 to 0010 1110 0101

1110 0101

Since the corry is not generated the negative. Find the 10's complement of the nexult to get the final nexult.

9's Complement of the nexult = 0100 1010

10'S complement of the result = 0100 1011

practice problem: perborm i) (48)10 - (19)10 ii) (52)10 - (81)10 in Excess-3 code using 10's complement.

Non weighted Codes: The non weighted Codes are not assigned with arry weight to each digit Position.

Enceys-3 Gode and gray code are the non weighted Godes.

#### Reflective code:

A neblective code is a binary code in which the n least significant bits for code words an through 2nd-1 are the mirror images for the code words for a through 2 -1. Rethertive code stample is gray code.

## Sequential code;

Sequential Code it one in which each succeeding code world is one binary number greater than it's preceeding code word. Ex: The Encert-3 code and 8421 code are the examples.

Gray code is a unit distance code. Because in this code Gray code any two code words differ in one bit Polition only.

The gray code is a reflective code also. Because the three least significant bits of (8) through (15), are the mirror images of those for (0) twough (7), in the case of four bit gray code.

For three bit gray code the two least significant bits for (4), through (7), are the misorar images of those for (0), through (3),

The gray code is used in the applications in which the normal sequence of binary numbers may produce an error (cr) ambiguity during the transition from one number to the next. For example if binary numbers are used, a change from 1111 to 1000 may broduce 1001 if the value of the right most bit takes longer time to change than the other three bits. The gray code elimenates this problem, because only one bit changes it's value during the transition between any two successive numbers.

the following table shows the gray code and binary code for decimal numbers of through 15.

## Binary to Gray code Conversion:

The binary to gray code conversion can be achieved using the following steps.

- ). The MSB of the gray Code is the same as the MSB of the given birrary number. So writedown MSB as it is.

- 2). To obtain the next gray digit, perborm the exclusive OR operation between the previous bit and Current binary bit and writedown the newlt

- 3). Repeat the Stepa until all binary bits have been exclusive oried with their previous ones.

Example: Convert 10111011 in binary into it's equivalent gray code.

sol) given Binary code 10111011

i. (10111011) = (11100110) gray.

Gray Codes.

### Gray code to binary conversion:

The gray code to binary conversion can be achieved using the following steps.

- i) The MSB of the binary number ix same as the MSB of the given gray code number. So corrite about the MSB as it is.

- 2) To obtain the next binary digit, perborn the exclusive or spendion between the bit just written down and the next gray code bit. write down the next.

- Repeat Hepe until all the gray code bits have been exclusive.

-ORED with bimony digits.

| A | В | A⊕B |

|---|---|-----|

| 0 | 0 | 0   |

| ٥ | 1 | 1   |

| r | O | ,   |

| t | 1 | 0   |

Fig: Exclusive or operation

Enample: Convert gray code 101011 into it's binary equivalent.

sol) give gray code is 101011.

M

Gray code:

Binary code:

:. (101011) = (110010) sinary

practice problem: convert i) (11100101) gray ii) (100110110) into binary

Generate a four-bit gray code sequence using mirror image property (i.e neblective property)

3 bit gray code 4-bit graycode 25it Gray code 000 0000 00 0001 001 0011 011 1 0 0010 010 110 0110 111 0111 101 0101 00 0100 1100

1 001

000

#### Alphanumeric Codes:

The Codes which consists of both numbers and alphabetic characters are called as alphanumenic codes. Most of these codes however, also represent symbols and various instructions necessary for conveying information.

The most commonly used alpha numeric codes are

- ) ASCII (American Standard code for Information Interchange)

- 2) EBCDIC (Extended Binary Coded Decimal Interchange Code)

the Standard binary code for the alphanumeric Characters is the ASCII code, which were 7 bits to code 128 characters. The 7 bits of the code are designated by b, through by with by as MSB. The ASCII code contains 94 graphic characters that can be Printed and 34 non printable characters that are used for various control functions.

The graphic characters consist of the 26 cuppercase letters (A through Z), the 26 lowercase letters (a through Z) the 10 numerals (o through 9) and 32 special printable characters but as 1, \* #, #;;

", \$ ctc.

0-9 (Numerals) 48 57

0110000 - 0111001

A-Z (uppercase letters) 65 90

1000001 - 1011010

a-Z (lowerase Letters) 97 122

1100001 - 1111010

the Control Characters are used for routing data and arranging the printed text into a prescribed format. There are three types of

- Control Characters. They are Format effectors, information seperators and communication control characters.

Format ebbectors: They are used to control the layout of printing En: Backspace, Horizontal Tab etc.

Into mation seperators: They are used to seperate the data into divisions such as paragraphs and pages. They include the characters such as record seperator (RS) and File seperator (FS) communication control characters: They are used to frame a text mexage transmitted trough a communication channel.

Ex: Start of Text (STX), End of text (ETX).

# EBCDIC Extended Binary Coded Decimal Interchange Code):

EBCDIC code is an 8-bit alphanumeric code. It is an 8-bit code that can code 256 characters. This code includes all the symbols and control characters that are present in ASCII. In addition to this, it includes many other symbols also.

Lower case a i j r 3 Z Letters 129 - 137 145 153 162 - 169 10000001 - 10001001 1001001 - 10011001 10100010 - 10101001

upper Case A I J R S Z letters 193 - 201 209 - 217 226 - 233 letters 11000001 11001001 1100010 - 1110 1001

Numerals 0 9 240 249

11110000 - 11111001

Encode the word BINARY in ASCII Code.

Sol.

B I N A R Y

66 73 78 65 82 89

100010 1001001 1000001 1010010 1011001

Practice problem: Convert the following into ASCII Codes

i) Capital City ii) NEW DELHI

## Error Detecting and correcting codes:

when the digital information in the binary form is Evansmitted from one system to another system, an evert may occur. This means a signal cooks ponding to 'o' may change to 'i' or vice versa due to the presence of noise. To maintain the data integrity between the transmitter and neceiver an entra bit (or) more than one bit one added to the data. These entra bits allow the detection and sometimes correction of the evert in the data. The data along with the entra bits forms the code.

The Codes which allow only evolor detection are called evolordetecting codes and the codes that allow evolor detection and Correction are called as evolor detecting and correcting codes.

Example for ever detecting and correcting code the example is - Hamming code.

## i) Passity bit method for ever detection:

\* A Poority bit in used for the purpose of detecting evoirs during the transmission of binary information.

A parity bit is an extrabit included with a binary message to make the number of 1's either odd (or) even. The message including the parity bit is transmitted and then checked at the receiving end to exorus. An error is detected if the checked Parity doesnot correspond with the one transmitted.

It called a parity generalor.

\* The circuit that checks the parity in the receiver is called Parity Checker.

\* In even parity the added parity bit will make the total number

of 1's as even, where as in odd parity the added parity sit will make the total number of 1's as odd.

The following table Shows a 3-bit message with even Parity and odd Parity.

| menage wit | th even parity | Message wi | the odd parity |

|------------|----------------|------------|----------------|

| Message    | Parity bit     | message    | parity bit     |

| 000        | 0              | 000        | 1              |

| 001        | 1              | 001        | 0              |

| 010        | 1              | 010        | Ö              |

| 011        | 0              | 011        | t              |

| 100        | 1              | 100        | 0              |

| 101        | 6              | 101        | 1              |

| 110        | ٥              | 110        | 1              |

| 1 1 [      | 1              | 111        | 0              |

Ex: Write the ASCII code for decimal digit 9 with an even parity. Place parity bit in the most significant position.

Sd) Decimal equivalent for the ASCII Code for 9 is (57)10, and it's ASCII code is 0111001.

To get the even posity for the ASCII ande ollool, the parity bit to be added is o'.

After adding Parity bit 'O' in MSB Position the code is 00111001.

Exi write the ASCII code for the alphabet A with an odd Parity.

Place the parity bit in the MSB Position.

IN) The decimal equivalent for the ASCII code of A is 65.

The ASCII code for A is = 1000001

To get odd Parity for the ASCII code 1000001, the Parity bit to be added ix i'. After adding the Parity bit in MSB Position the code becomes 11000001

After receiving the mexage with parity bit at the receiver, the receiver checks for the Concensured Parity. If there is an evolution the Parity the receiver will request the transmitter to re-send the mexage.

# ii) Hamming code for cover detection and correction:

Hamming code not only provided the detection of a bit esonor but also identifies which bit it in evert so that it can be corrected. Hence the hamming Code is Called as evert detecting and evert correcting ade. The Code uses a number of parity bits botated at certain positions in the Code group.

The number of parity bits to be included depends on the number of information bits. If the number of information bits is designated as x, then the number of parity bits 'p' is determined by the following relationship.

for example if we have a 4-bit message i.e x=4 then P is found by trial and evisit using the above equation. Let P=2, then  $2^2=2^2=4$  and 24P+1=4+2+1=7

Since  $2^p$  must be equal to be greater than x+p+1, the relationship in equation (1) is not satisfied. Hence we have to try with next value of p. Let p=3.

Then  $2^P = 2^3 = 8$  and x+P+1 = 4+3+1 = 8

This value of p satisfies the relationship given in equation (1) therefore we can say that three party bits are recurred to provide single error correction for fown information bits.

### Locations of the passity bits in the hamming code:

The parity bits one located in the positions of ascending powers of 2 i.e. 2, 2, 2, 23. ... (i.e.1, 2, 4, 8, ---). Therefore for 7-bit code, locations for parity bits and information bits are Shown below.

7 6 5 4 3 2 1 Da Da Da P4 D3 P2 P1 where symbol Pn designates a particular parily Lit and In designates a Particular information bit and n is the Location number

Let us see how to determine the Value of each Parity bit. To do this we must write the binary number for each decimal location number as shown in table below.

| Bit Designation                          | P   | DG  | 05  | P4  | 03 | P2  | P,  |

|------------------------------------------|-----|-----|-----|-----|----|-----|-----|

| Bit Location                             | 7   | ۵   | 5   | 4   | 3  | 2   | ,   |

| Binary equivalent of the bit Location no | 111 | 110 | 101 | 100 | on | 010 | 001 |

| Information bits                         |     |     |     |     |    |     |     |

| Parity bits                              |     |     |     |     |    |     |     |

Assignment of P,: Looking at the table, we can see that Parity bit P, has a 1 in it's rightmost digit. This Pavity bit Unecks all the bit Locations including itself that have its in the same location. Therefore Parity bit P, checks bit locations 1, 3, 5, 7 and assigns P, according to even or odd Parity. For even parity hamming Code, it assigns P, such that bit locations 1, 3, 5 and 7 will have even Parity.

Assignment of P2: Looking at the lable, coe can see that the Parity bit P2 has a 1 in it's middle bit Position. This Parity bit checks all the bit locations including itself that have 1's in the middle bit. Therefore, Parity bit P2 checks the bit locations 2,3,6,7 and assigns P2 according to even or odd Parity.

Assignment of P4'. Looking at the table, we can see that the pavily bit P4 has a 'I' in it's debt most bit Position. This Pavily bit checks all the bit locations including itself that have 1's in the lebt most bit. Therefore Pavilty bit 14 checks the bit locations 4,5,6 and 7 and assigns P4 according to even or odd Pavilty

Example: Encode the binary word 1011 into 7-bit even parity hamming

Sty step1> Given meusage = 1011, number of information bits = x = 4 Let the number of parity bits required be P, then it should satisfy 2" > x+P+1.

P=3 Satisfies the above Condition.

Since the given message bits one 4, abten including 3 party bits hamming code will have 4+3=7 bits.

| Bit Designation                       | Da  | De  | D <b>5</b> | P4  | D <sub>3</sub> | P   | P, |

|---------------------------------------|-----|-----|------------|-----|----------------|-----|----|

| Bit Location                          | 7   | 6   | 5          | 4   | 3              | 2   |    |

| Binary savivalent of the bit location | 111 | 116 | 101        | 100 | 011            | 010 | 00 |

| Information bits                      | 1   | Ö   | 1          |     | 1              |     |    |

| Parity bits                           |     |     |            | O   |                | 0   | 1  |

fig: Bit location table.

step3) beteamine the Pavity bits.

For P,: Bit locations 3,5 and 7 have three 1's and therefore to have an even parity P, must be 1.

FOY P2: Bit locations 3,6 and 7 have two 1's and therefore to have an even parity of must be o'.

For P4: Bit locations 5, 6 and 7 have two is and therefore to have an even parity of must be o'.

(step4) Enter the passity bits into the table to form a 7-bit hamming code 1010101.

practice problem: Determine the hamming code for a binary merrage 1101 Using even parity.

## Detecting and Correcting an evid wing hamming code:

there we will see how to use a hamming code to locate and correct an error. To do this each pavily lit along with it's group of bits must be checked for proper parity. The correct nexult of individual parity check is marked as o' where as whong nexult of parity check is marked by '1'. After all Parity checks, a binary word is formed taking the bit of P, as LSB. The binary word formed like this, gives the bit location where ever has occured. If the binary word has all o's then there is no ever in the hamming code.

Example: Assume that the even parity hamming code in the previous example is (1010101) is transmitted and 1000101 is necessed. The necesser obesnot know what was transmitted. Determine bit location where example has occurred using the necessed Code:

sol) step1: Construct bit location table

| Bit designation   | DF | P6  | D5  | P4  | D3  | Pz  | P.  |

|-------------------|----|-----|-----|-----|-----|-----|-----|

| Bit Location      | 7  | B   | 5   | 4   | 3   | 2   | l   |

| Binary equivalent | ŧη | 110 | 101 | 100 | DII | 010 | 001 |

| Received Gode     | ĺ  | 0   | Ò   | ٥   | 1   | 0   | T   |

Step 2: Check for parity bits.

there are three 1's in the group of 1,3,5,7.

:. Parity checks for even parity is wrong. => 1 (LSB)

For P2: P2 checks the locations 2, 3, 6, 7

There are two I's in the group of 2,3,6,7.

- is parity checks for even parity is correct. => 0

- For Py: Py checks the docations 4,5,6,7.

There is only one 1 in the group of 4,5,6,7.

(34)

i. The resultant world is 101. This says that the bit in the bit location 5 is in evolut. In the necessed Gode it is o'. Hence it should be corrected as 1.

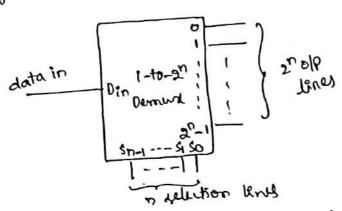

:. The Corrected Code is 1010101.